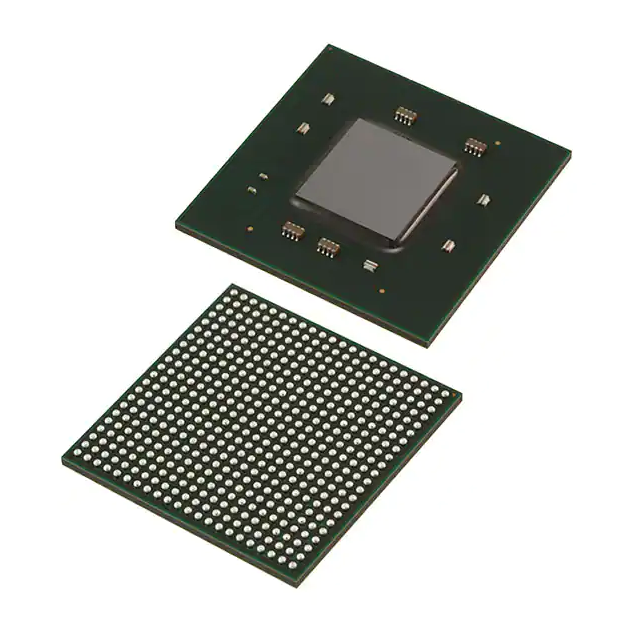

Novo i originalno XC7A100T-2FGG484I IC integrirano kolo FPGA polje programabilno polje vrata ad8313 IC FPGA 285 I/O 484FBGA

Atributi proizvoda

| TYPE | OPIS |

| Kategorija | Integrisana kola (IC)Embedded |

| Proiz | AMD Xilinx |

| Serije | Artix-7 |

| Paket | Tray |

| Standard Package | 60 |

| Status proizvoda | Aktivan |

| Broj LAB-ova/CLB-ova | 7925 |

| Broj logičkih elemenata/ćelija | 101440 |

| Ukupan broj RAM bitova | 4976640 |

| Broj I/O | 285 |

| Napon – napajanje | 0,95 V ~ 1,05 V |

| Vrsta montaže | Surface Mount |

| Radna temperatura | -40°C ~ 100°C (TJ) |

| Paket / Case | 484-BBGA |

| Paket uređaja dobavljača | 484-FBGA (23×23) |

| Osnovni broj proizvoda | XC7A100 |

Korištenje FPGA kao procesora prometa za sigurnost mreže

Saobraćaj do i od sigurnosnih uređaja (firewall) je šifriran na više nivoa, a L2 enkripcija/dešifriranje (MACSec) se obrađuje na mrežnim čvorovima sloja veze (L2) (prekidači i ruteri).Obrada izvan L2 (MAC sloja) obično uključuje dublje raščlanjivanje, L3 dešifriranje tunela (IPSec) i šifrirani SSL promet s TCP/UDP prometom.Obrada paketa uključuje raščlanjivanje i klasifikaciju dolaznih paketa i obradu velikih količina saobraćaja (1-20M) sa velikom propusnošću (25-400Gb/s).

Zbog velikog broja potrebnih računarskih resursa (jezgri), NPU-ovi se mogu koristiti za relativno veću brzinu obrade paketa, ali nisko kašnjenje, skalabilna obrada prometa visokih performansi nije moguća jer se promet obrađuje korištenjem MIPS/RISC jezgara i zakazivanjem takvih jezgara na osnovu njihove dostupnosti je teško.Upotreba sigurnosnih uređaja zasnovanih na FPGA može efikasno eliminisati ova ograničenja CPU i NPU baziranih arhitektura.

Sigurnosna obrada na nivou aplikacije u FPGA

FPGA su idealni za inline sigurnosnu obradu u zaštitnim zidovima nove generacije jer uspješno zadovoljavaju potrebu za većim performansama, fleksibilnošću i malim kašnjenjem.Osim toga, FPGA također mogu implementirati sigurnosne funkcije na nivou aplikacije, koje mogu dodatno uštedjeti računarske resurse i poboljšati performanse.

Uobičajeni primjeri sigurnosne obrade aplikacija u FPGA uključuju

- TTCP motor za istovar

- Podudaranje regularnog izraza

- Asimetrična enkripcija (PKI) obrada

- TLS obrada

Sigurnosne tehnologije sljedeće generacije koje koriste FPGA

Brojni postojeći asimetrični algoritmi su ranjivi na kompromitaciju od strane kvantnih kompjutera.Asimetrični sigurnosni algoritmi kao što su RSA-2K, RSA-4K, ECC-256, DH i ECCDH su najviše pogođeni tehnikama kvantnog računanja.Istražuju se nove implementacije asimetričnih algoritama i NIST standardizacije.

Trenutni prijedlozi za postkvantnu enkripciju uključuju metodu Ring-on-Error Learning (R-LWE) za

- Kriptografija javnog ključa (PKC)

- Digitalni potpisi

- Kreiranje ključa

Predložena implementacija kriptografije javnog ključa uključuje određene dobro poznate matematičke operacije (TRNG, Gausov uzorkivač šuma, sabiranje polinoma, dijeljenje kvantifikatora binarnog polinoma, množenje, itd.).FPGA IP za mnoge od ovih algoritama je dostupan ili se može efikasno implementirati korištenjem FPGA građevnih blokova, kao što su DSP i AI motori (AIE) u postojećim i Xilinx uređajima sljedeće generacije.

Ova bijela knjiga opisuje implementaciju L2-L7 sigurnosti korištenjem programabilne arhitekture koja se može primijeniti za ubrzanje sigurnosti u rubnim/pristupnim mrežama i vatrozidima sljedeće generacije (NGFW) u poslovnim mrežama.